임베디드 스터디 - 동기 순서논리회로의 설계

임베디드 스터디 - 동기 순서논리회로의 설계

이번 글 참고자료:

한빛아카데미, 디지털 논리회로4판

A digital logic designer and circuit simulator. Contribute to hneemann/Digital development by creating an account on GitHub.

순서논리회로의 해석

- 순서논리회로는 다음 해석 절차를 통해 회로의 동작을 이해할 수 있다.

- 회로 입력과 출력에 변수 명칭 부여

- 조합논리회로가 있으면, 조합논리회로의 불 대수식 유도

- 회로의 상태표(State table) 작성

- 회로의 상태표를 바탕으로 상태도(State diagram) 작성

- 상태 방정식 유도

- 상태표와 상태도를 바탕으로 회로의 동작 설명

- 순서논리회로를 해석하는 과정에서 셋업, 홀드 타임 등의 물리적 요건은 모두 충족한다고 가정하고 해석한다.

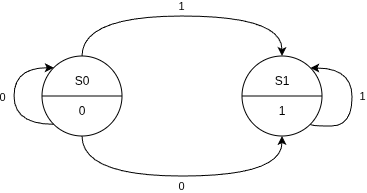

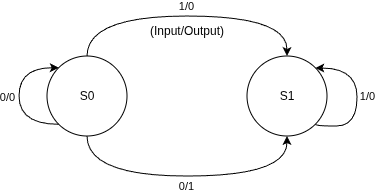

상태도 (State diagram)

순서논리회로의 동작 형태에 따라 상태도를 표현하는 방법이 2가지 있다.

플립플롭 여기표 (Excitation table)

- 현재 상태에서 다음 상태로 전환되기 위한 입력의 조건표이다. 특성표와는 다음 차이가 있다.

- 특성표 : 현재 상태와 입력값을 바탕으로 다음 상태를 표시

- 여기표 : 현재 상태와 다음 상태를 바탕으로 요구되는 입력값을 표시

SR-FF 여기표

| 현재 상태($Q_{t}$) | 다음 상태($Q_{t+1}$) | 입력($S$) | 입력($R$) |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | X | 0 |

JK-FF 여기표

| 현재 상태($Q_{t}$) | 다음 상태($Q_{t+1}$) | 입력($J$) | 입력($K$) |

|---|---|---|---|

| 0 | 0 | 0 | X |

| 0 | 1 | 1 | X |

| 1 | 0 | X | 1 |

| 1 | 1 | X | 0 |

D-FF 여기표

| 현재 상태($Q_{t}$) | 다음 상태($Q_{t+1}$) | 입력($D$) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

T-FF 여기표

| 현재 상태($Q_{t}$) | 다음 상태($Q_{t+1}$) | 입력($T$) |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

순서논리회로의 설계

- 순서논리회로는 다음 설계 과정을 거쳐 회로를 구성할 수 있다.

- 회로 동작 기술(상태도 작성)

- 회로의 상태표 작성

- 상태 축소 및 상태 할당

- FF의 수와 종류 결정

- 회로의 입력과 출력에 변수명 부여

- 회로의 여기표 작성

- 회로 간소화를 통한 회로의 출력 함수 유도

- 순서논리회로도 작성

상태 축소

- 설계 과정에서 외부 입출력에 대한 요구 조건을 유지한 상태에서 플립플롭의 수를 줄이는 절차.

- 각각의 상태에 대해 입력에 따른 출력과 상태 변화가 동일한 경우, 해당 상태는 등가 상태이므로 상태를 축소할 수 있다.

상태 할당

- 설계 과정에서 주어진 임의의 상태에 대해 이진 코드로 데이터를 할당하는 과정이다.

- $2^{m-1} < (시스템의 상태의 개수) < 2^{m}$인 경우, 회로에서 $m$개의 FF로 회로를 구성하여 각각의 상태에 이진 코드를 부여한다.

미사용 상태의 설계

- 상태 할당 이후 FF의 수에 따라 남는 상태가 발생하는 경우, 해당 상태를 다른 활성 상태로 전환되도록 처리한다.

- 외란에 의한 상태 전환, 오류에 따른 상태 전환이 발생할 경우를 대비한 강건 시스템 설계 요소 중 하나이다.

이 기사는 저작권자의 CC BY 4.0 라이센스를 따릅니다.