임베디드 스터디 - 메모리 - 2

임베디드 스터디 - 메모리 - 2

이번 글 참고자료:

한빛아카데미, 디지털 논리회로4판

ElectronicsTutorials

A digital logic designer and circuit simulator. Contribute to hneemann/Digital development by creating an account on GitHub.

플래시 메모리

- EEPROM의 한 종류. 비휘발성인 ROM의 장점과 데이터 입출력이 자유로운 RAM의 장점을 갖춘 메모리.

- 반도체 내부 전자 회로 구성에 따라 NAND, NOR 플래시로 구분한다.

- NAND 플래시 : 메모리 셀을 수직으로 배열함. 대용량화, 쓰기 및 지우기 속도에 유리하다.

- NOR 플래시 : 메모리 셀을 수평으로 배열함. 읽기 속도에 유리하다.

플래시 메모리셀

- 플래시 메모리는 FGMOS(Floating Gate MOSFET)이라는 MOSFET 소자에 전하를 축적하여 데이터를 저장한다.

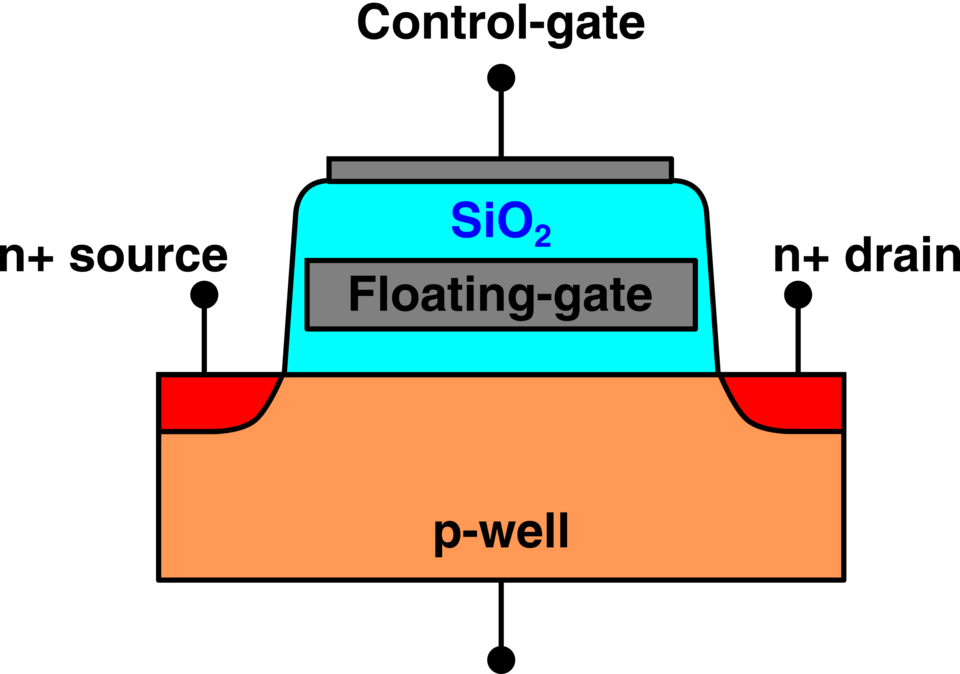

- FGMOS 구조

- 제어 게이트(Control Gate) : 메모리셀의 워드라인(WL)역할도 겸한다.

- ONO(Oxide-Nitride-Oxide) 절연막

- 플로팅 게이트(Floating Gate) : 주위가 모두 전기적으로 절연되어 Floating 상태임.

- 드레인 (Drain)

- 소스 (Source)

- FGMOS 동작

- 제어 게이트에 전압을 인가하여 플로팅 게이트에 전자를 저장한다. 플로팅 게이트에 저장된 전자가 많으면 논리 0, 적거나 없으면 논리 1이다. MOSFET과 동일하게 플로팅 게이트의 전하량에 따라 드레인과 소스 사이에 전류가 흐르는 Threshold voltage($V_t$)가 변한다.

플래시 메모리 동작

- 쓰기 : 제어 게이트에 12~19V를 인가하여 플로팅 게이트에 전자를 채운다. 초기에는 플로팅 게이트에 전자가 없는 논리 1 상태로 유지된다.

- NAND 플래시에서 이를 터널 주입(Tunnel Injection), NOR 플래시에서 이를 Hot-electron Injection이라 한다.

- 읽기 : 제어 게이트에 5V를 인가하여 메모리셀을 동작시킨다.

- 플로팅 게이트에 전자가 채워져있을 경우(논리 0), 플로팅 게이트에 축적된 전자가 FGMOS의 문턱전압($V_{t}$)을 높여, 읽기 전압(~5V)이 $V_t$에 미치지 못하므로, 소스-드레인 사이에 채널이 형성되지 않는다.

- 반대로 플로팅 게이트에 전자가 없을 경우(논리 1), 소스-드레인 사이에 채널이 형성되어 전류가 흐른다.

- 지우기 : 제어 게이트에 0V, P+(P-well)와 N층에 20V의 전압을 가하여 플로팅 게이트에서 전자를 빼낸다.

- NAND 플래시에서 이 과정을 터널 릴리스(Tunnel Release), NOR 플래시에서 이를 F-N 터널링 (Fowler-Nordheim Tunneling)이라 한다.

플래시 메모리 구조

- 스트링(String) : 직렬로 연결된 32~64개의 메모리 셀의 묶음으로, 플래시 메모리의 최소 회로 단위

- 페이지(Page) : 동일 워드라인에 연결된 셀들의 집합으로, 읽기·쓰기의 최소 단위 (일반적으로 4KB~16KB)

- 블록(Block) : 여러 페이지(64~256개)의 묶음으로, 소거(Erase)의 최소 단위 (페이지 단위 쓰기, 블록 단위 소거)

- 어레이(Array) : 다수의 블록이 모인 전체 메모리 구조로, 하나의 NAND 플래시 칩을 구성하는 최상위 단위

NAND 플래시

- 워드 라인이 서로 인접하게 구성되며, 같은 비트에 연결된 FGMOS끼리 소스와 드레인을 공유하는 형태로 구성된다.

- NAND 플래시의 셀 면적 크기는 DRAM과 NOR 플래시 셀 면적 크기보다 작다.

- NAND 플래시는 페이지 단위의 순차 접근(Sequential Access) 방식에서 빠른 쓰기 성능을 갖는다.

NOR 플래시

- 각각의 메모리셀이 독립적으로 구성되어 있으며, 메모리셀 비트 선 접속부와 소스 선 접속부가 각각 따로 구성되어 NAND보다 저장 밀도가 낮다.

- NOR 플래시는 바이트/워드 단위의 랜덤 접근(Random Access) 방식으로 빠른 읽기 성능을 갖는다.

NAND vs NOR

| 구분 | NAND Flash | NOR Flash |

|---|---|---|

| 셀 연결 방식 | 직렬(NAND) | 병렬(NOR) |

| 접근 방식 | 순차 접근 (랜덤 접근 불가) | 랜덤 접근 가능 |

| XIP 지원 | ❌ 불가 | ✅ 가능 (코드 직접 실행) |

| 읽기 속도 | 느림 | 빠름 |

| 쓰기 속도 | 빠름 | 느림 |

| 소거 단위 | 블록 (수백 KB) | 섹터 (수십 KB~수백 KB) |

| 소거 속도 | 빠름 | 느림 |

| 쓰기 수명 | 약 10만 회 | 약 1만 회 |

| 불량 섹터 | 출하 시 존재 가능, BBT(Bad Block Table)로 관리 필수 | 출하 시 불량 섹터 없음 |

| 집적도 | 높음 (소형·대용량 유리) | 낮음 |

| 비용 | 저가 | 고가 |

| 주요 용도 | 대용량 데이터 저장 (eMMC, SSD, SD카드) | 부트로더·펌웨어 코드 저장 |

| 대표 인터페이스 | ONFI, Toggle | CFI |

메모리셀 저장 방식

- 제어 게이트에 인가하는 전압에 따라 플로팅 게이트에 주입하는 전자가 다르기에, 이를 바탕으로 메모리셀에 데이터를 저장하는 방식이 다양하게 존재한다.

- SLC (Single Level Cell) : 1셀에 1비트를 저장

- MLC (Multi Level Cell) : 1셀에 2비트를 저장

- TLC (Triple Level Cell) : 1셀에 3비트를 저장

| 구분 | SLC | MLC | TLC |

|---|---|---|---|

| 정식 명칭 | Single Level Cell | Multi Level Cell | Triple Level Cell |

| 셀당 저장 비트 | 1bit | 2bit | 3bit |

| 전압 레벨 수 | 2 (0/1) | 4 | 8 |

| 읽기 속도 | 빠름 | 중간 | 느림 |

| 쓰기 속도 | 빠름 | 중간 | 느림 |

| 쓰기 수명 | 약 10만 회 | 약 1만 회 | 약 3천 회 |

| 신뢰성 | 높음 | 중간 | 낮음 |

| 집적도 | 낮음 | 중간 | 높음 |

| 비용 | 고가 | 중간 | 저가 |

| 주요 용도 | 산업용·항공우주·군용 | 엔터프라이즈 SSD | 소비자용 SSD·스마트폰 |

이 기사는 저작권자의 CC BY 4.0 라이센스를 따릅니다.