임베디드 스터디 - CPU

임베디드 스터디 - CPU

이번 글 참고자료:

정익사, 컴퓨터 구조의 이해

CPU (Central Processing Unit)

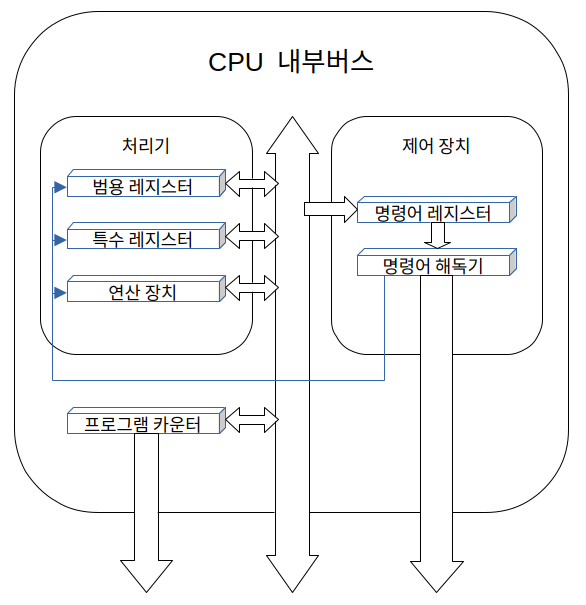

- 중앙 처리 장치(CPU)의 기능은 메모리의 프로그램을 읽어 명령어를 해석하고, 해석된 명령을 수행하는 것이다.

- CPU는 다음과 같이 구성된다.

- 제어 장치 (CU, Control Unit)

- 처리기 (PU, Processor Unit)

- 연산 장치 (ALU, Arithmetic Logical Unit)

- 범용 레지스터 (GPR, General Purpose Register)

- 특수 레지스터 (SFR, Special Function Register)

범용 레지스터

- 프로그램의 진행 도중 수시로 사용되는 데이터, 연산 결과를 일시적으로 기억하는데 사용되는 기억 장치

- CPU의 종류에 따라 범용 레지스터의 구조는 다양하지만, 기본적으로 여러 레지스터를 묶어 구성된다.

특수 레지스터

- 특수 레지스터는 각각의 역할이 고정되어 있다.

- 프로그램 카운터(PC, Program Counter) : 현재 처리하려는 데이터가 저장되어 있는 메모리의 주소를 지정하는 레지스터, 데이터 인출 후 자동으로 다음 수행할 명령어 주소를 지정한다.

- Increment(다음 주소 지정), Load(명령어 주소 저장) 기능으로 구성됨

- 명령어 레지스터(IR, Instruction Register) : 명령어를 기억하는 레지스터. 명령어 해독기에서 명령 해독 후 제어 신호로 사용된다.

- 누산기(Accumulator) : 산술 논리 연산에서 오퍼랜드나 연산 결과를 일시적으로 저장하는 레지스터

- 스택(Stack) : 범용 레지스터, 프로그램 카운터 등의 내용을 일시적으로 저장하는 장치. LIFO(Last In First Out) 구조.

- 스택 포인터(SP, Stack Pointer) : 스택의 최상단(top) 주소를 가리키는 레지스터

- 스택 영역 : 실질적으로 데이터를 저장하는 레지스터

- 프로그램 카운터(PC, Program Counter) : 현재 처리하려는 데이터가 저장되어 있는 메모리의 주소를 지정하는 레지스터, 데이터 인출 후 자동으로 다음 수행할 명령어 주소를 지정한다.

명령 수행

- CPU의 명령은 3가지 동작으로 사이클을 이룬다.

- Fetch : PC가 가르키는 주소에서 명령어를 가져온다.

- Decode : 명령어를 해독한다.

- Execute : 해독한 명령어를 바탕으로 연산을 수행한다.

- 그 외 Interrupt, Indirect Cycle이 있다.

- Interrupt : 명령 실행 중 외부 장치(입출력 장치 등)에 의해 인터럽트가 들어오면 그에 맞는 서비스를 제공

- Indirect : 명령어가 간접 주소 지정 방식일 때 유호 주소를 읽어 들이는 사이클

레지스터 전송

- 레지스터 혹은 메모리에 저장되어 있는 이진 데이터를 전송하는 작업

- 하나의 레지스터 전송 실행 동작을 하나의 마이크로 오퍼레이션(Micro Operation)이라고 함

- 레지스터 전송에는 다음과 같은 용어를 사용한다.

- 이진수 정보 : 레지스터 내부에 저장되는 이진수

- 마이크로 오퍼레이션 : 한 개의 클록 펄스에 실행되는 동작

- 제어 함수 : 한 번에 한 개의 오퍼레이션을 순차적으로 실행하는 기능

레지스터 전송 언어 : 레지스터 동작을 표현하는 기호

기호 의미 예시 문자와 숫자 레지스터를 나타냄 $A$, $MBR$, $R3$ 첨자 레지스터의 비트 $A_2$ 화살표 데이터의 전송 $A$ ← $B$ 콜론 (:) 제어 함수 표시 $P:$ , $X’T0:$ 콤마 (,) 두 마이크로 오퍼레이션 구분 $A$ ← $B$ , $B$ ← $A$ 소괄호 레지스터의 부분 표시 $I(1-5)$, $MBR(AD)$ 대괄호 메모리 전송에 쓰이는 번지를 표시 $MBR ← M[MAR]$

직렬 전송

- 레지스터의 내용을 시프트하며 한 번에 한 비트씩 전송하는 동작

- 4bit 레지스터 B에서 4bit 레지스터 A로의 직렬 전송은 다음과 같은 오퍼레이션을 수행한다.

- $A_1$ ← $B_4$, $B_1$ ← $B_4$, $A_i$ ← $A_{i-1}$, $B_i$ ← $B_{i-1}$, $i=2, 3, 4, \cdots$

- 시프트 레지스터의 동작을 레지스터 전송 언어로 표헌한 내용이다.

병렬 전송

- 레지스터의 내용을 한 클럭 펄스 동안 동시에 병렬로 전송하는 동작

- 포인트 투 포인트 전송

- 특정한 레지스터에서 지정된 레지스터로 단일 전송하는 동작

- $xT_{1}$ : $A$ ← $B$

if ($x$ and $T_{1}$) then ($A$ ← $B$)

- $xT_{1}$ : $A$ ← $B$

- 특정한 레지스터에서 지정된 레지스터로 단일 전송하는 동작

- 멀티 포인트 전송

- 여러 개의 레지스터들로부터 특정한 레지스터로 데이터를 전송하는 동작

- Multiplexer-based transfer 라고도 함

- 2개의 레지스터 $A$,$B$에서 레지스터 $C$로의 멀티 포인트 전송은 다음과 같이 동작한다.

- if ($T_{1} = 1$) then ($C$ ← $A$) else if ($T_{2} = 1$) then ($C$ ← $B$)

$T_{1}$ : $C$ ← $A$

$T_{2}$ : $C$ ← $B$

- if ($T_{1} = 1$) then ($C$ ← $A$) else if ($T_{2} = 1$) then ($C$ ← $B$)

- 버스 전송

- 여러 개의 레지스터가 공통의 버스 선을 공유하면서 상호 간 데이터를 전송하는 동작

- 포인트 투 포인트, 멀티 포인트보다 경제적이다.

이 기사는 저작권자의 CC BY 4.0 라이센스를 따릅니다.