임베디드 스터디 - 논리 게이트

임베디드 스터디 - 논리 게이트

이번 글 참고자료: 한빛아카데미, 디지털 논리회로4판

각종 논리게이트

논리 레벨

- 회로 소자에 따라

High(1),Low(0)를 인식하는 전압 영역이 다르다.

| $논리값 \setminus 회로소자$ | TTL | CMOS |

|---|---|---|

| HIGH | $2.5V$ ~ $5V$ | $3.5V$ ~ $5V$ |

| UNDEFINED | $0.8V$ ~ $2.5V$ | $1.5V$ ~ $3.5V$ |

| LOW | $0V$ ~ $0.8V$ | $0V$ ~ $1.5V$ |

논리게이트

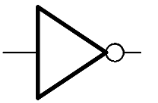

NOT 게이트 : 논리 반전, 인버터(Inverter)

$F = \overline{A}$

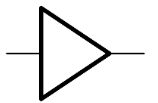

입력($A$) 출력($F$) 0 1 1 0 BUFFER 게이트 : 논리 지연, 전압 정류화

$ F = A $

입력($A$) 출력($F$) 0 0 1 1 TRI-STATE BUFFER 게이트 : 입력값에 대한 출력 제어

입력($A$) 입력($E$) 출력 ($B$) 0 0 $Z$(High Impedence) 1 0 $Z$(High Impedence) 0 1 0 1 1 1 AND 게이트 : 논리 곱

$ F = A \cdot B $

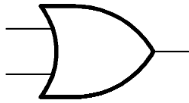

입력($A$) 입력($B$) 출력 ($F$) 0 0 0 0 1 0 1 0 0 1 1 1 OR 게이트 : 논리 합

$ F = A + B $

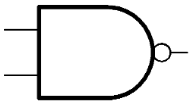

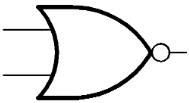

입력($A$) 입력($B$) 출력 ($F$) 0 0 0 0 1 1 1 0 1 1 1 1 NAND 게이트 : 논리 곱의 부정

$F = \overline{A \cdot B}$

입력($A$) 입력($B$) 출력 ($F$) 0 0 1 0 1 1 1 0 1 1 1 0 NOR 게이트 : 논리 합의 부정

$F = \overline{A + B}$

입력($A$) 입력($B$) 출력 ($F$) 0 0 1 0 1 0 1 0 0 1 1 0 XOR 게이트 : 배타적 논리 합

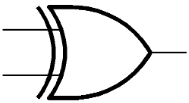

$F = A \oplus B$

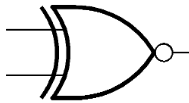

입력($A$) 입력($B$) 출력 ($F$) 0 0 0 0 1 1 1 0 1 1 1 0 XNOR 게이트 : 배타적 논리 합의 부정

$F = \overline{A \oplus B}$

입력($A$) 입력($B$) 출력 ($F$) 0 0 1 0 1 0 1 0 0 1 1 1

범용 게이트 (Universal Gates)

- 단일 종류의 게이트만으로 모든 게이트를 구현할 수 있다.

- NAND, NOR 게이트가 Universal Gates 이다.

정논리(Positive Logic), 부논리(Negative Logic)

- 정논리 : 전압이 High $(5V)$ 일 때 논리 1, 전압이 Low $(0V)$ 일 때 논리 0

부논리 : 전압이 High $(5V)$ 일 때 논리 0, 전압이 Low $(0V)$ 일 때 논리 1

- 정논리와 부논리의 상호 변환은 입출력 단에 모두 NOT을 추가하여 변환할 수 있다.

이 기사는 저작권자의 CC BY 4.0 라이센스를 따릅니다.