임베디드 스터디 - 조합논리회로 - 1

이번 글 참고자료:

한빛아카데미, 디지털 논리회로4판

ElectronicsTutorials

조합논리회로

기본 논리게이트를 조합하여 더욱 복잡한 연산과 스위칭 기능을 구현하는 회로

Universal Logic으로 모든 회로 구성을 표현할 수 있다.

- 조합논리회로의 동작을 표현하기 위해서는 3가지 표현 방법을 사용한다.

- 불 대수

- 진리표

- 로직 다이어그램

- 조합논리회로는 입력 $n$개에 대해 $2^{n}$개의 입력 조합을 진리표를 나타내고, 서로 다른 $m$개의 출력을 생성하기 위해 $m$개의 논리 함수가 필요하다.

조합논리회로 분류

- 대수 & 로직 연산

- 가산기(Adders)

- 감산기(Subtractors)

- 비교기(Comparitors)

- 데이터 전송

- 멀티플렉서(Multiplexers)

- 디멀티플렉서(Demultiplexers)

- 인코더(Encoders)

- 디코더(Decoders)

- 코드 변환

- Gray Code 변환기

- BCD 변환기

- 7-세그먼츠

- 오류 검출

- 패리티 생성기

- 패리티 검출기

- 에러수정코드

가산기

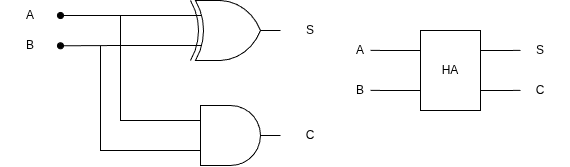

반가산기 (Half Adder)

반가산기는 한 자리 2진수 2개를 입력하여 합$(S)$과 캐리$(C)$의 출력을 갖는 덧셈 회로이다.

불 대수 함수

$S=A\oplus B$

$C=A \cdot B$진리표

입력($A$) 입력($B$) 출력($S$) 출력($C$) 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1

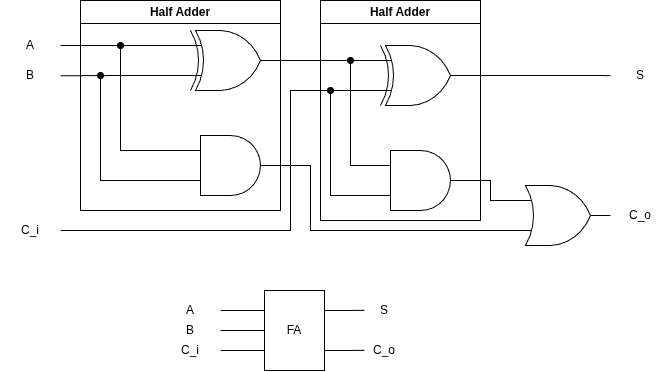

전가산기 (Full Adder)

전가산기는 한 자리 2진수 2개와 이전 자릿수의 캐리$(C_{i})$를 입력하여 합$(S)$과 다음 자릿수로의 캐리$(C_{o})$의 출력을 갖는 덧셈 회로이다.

전가산기는 2개의 반가산기를 활용하여 회로를 구성할 수 있다.

불 대수 함수

$S=A\oplus B \oplus C_{i}$

$C_{o}=C_{i} \cdot (A \oplus B) + A \cdot B$진리표

입력($A$) 입력($B$) 입력($C_{i}$) 출력($S$) 출력($C_{o}$) 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

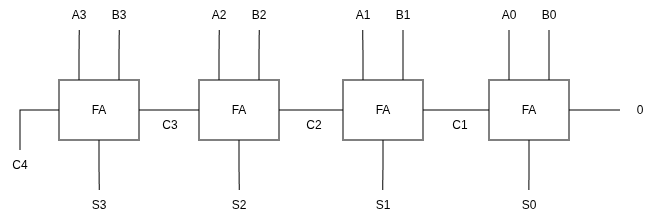

4-Bit 병렬 가산기

전가산기 여러 개를 병렬로 연결하여 2비트 이상의 가산기를 생성할 수 있다. 4-Bit 병렬 가산기는 다음과 같은 형태로 구성된다.

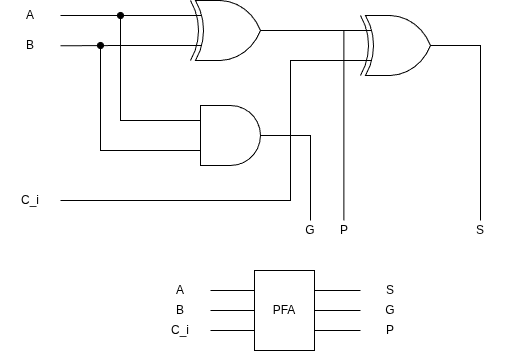

부분 전가산기 (Partial Full Adder)

전가산기 기반의 병렬 가산기는 이전 가산기에서 다음 가산기로 넘어가는 캐리 연산에 의해 전체 연산 속도가 느린 단점이 있다. (리플 캐리(Ripple-Carry) )

이러한 단점을 해결하기 위해, 캐리의 결과값을 기존 논리식으로부터 예측하여 연산하는 캐리 예측 연산 회로를 사용한다.

부분 전가산기는 기존 전가산기를 수정하여 Generate$(G)$ Propagate$(P)$를 추가 출력을 생성하여 캐리 예측 신호를 출력한다.

불 대수 함수

$S=A\oplus B \oplus C_{i}$

$G = A \cdot B$

$P = A \oplus B$

$C_{o}=C_{i} \cdot (A \oplus B) + A \cdot B = C_{i} \cdot P + G$

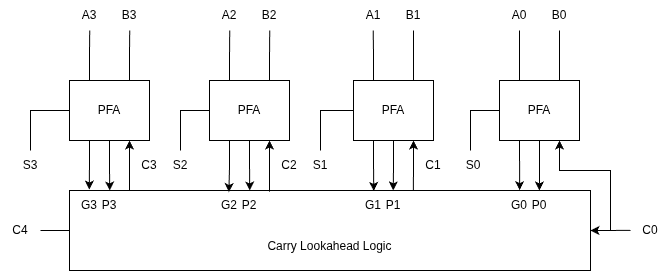

4-Bit 캐리 예측 가산기 (CLA, Carry Lookahead Adder)

4-Bit 병렬 가산기의 구성과 유사하게, 병렬로 연결된 PFA 4개와 캐리 예측 로직(Carry Lookahead Logic)을 조합하여 회로를 구성한다.

캐리 예측 로직은 대표적으로 74182 IC가 있다.

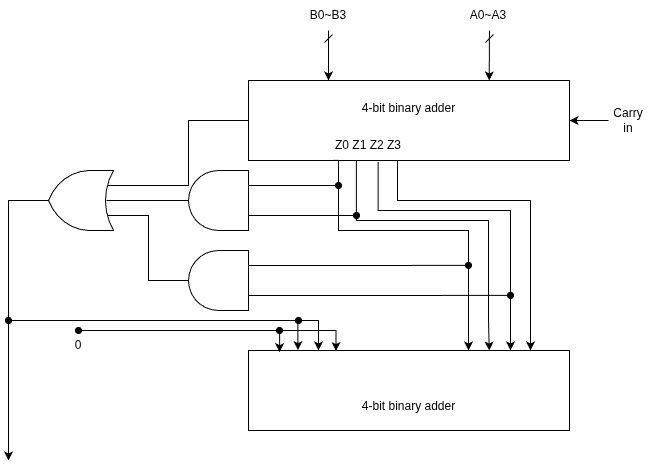

BCD 가산기

BCD 코드는 10진수의 자리수를 2진수로 표현한다는 점에서 기본 2진수 연산에서 추가적인 보정이 필요하다.

4-Bit BCD 가산기는 4-Bit 병렬 가산기와 BCD 보정 회로를 활용하여 회로를 구성할 수 있다.

감산기

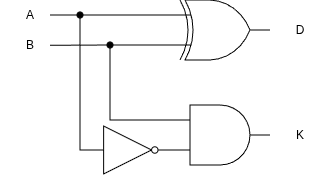

반감산기 (Half Subtractor)

반감산기는 한 자리 2진수 2개를 입력하여 차$(D)$과 빌림수$(K)$의 출력을 갖는 뺄셈 회로이다.

감산기에서 빌림수(Borrow)는 2개의 2진수로 자연수 영역에서 뺄셈을 표현할 수 없을 때, 윗 자리의 수를 빌려와 연산했음을 확인하는 출력값이다.

불 대수 함수

$D=A\oplus B$

$K=\overline{A} \cdot B$진리표

입력($A$) 입력($B$) 출력($D$) 출력($K$) 0 0 0 0 0 1 1 1 1 0 1 0 1 1 0 0

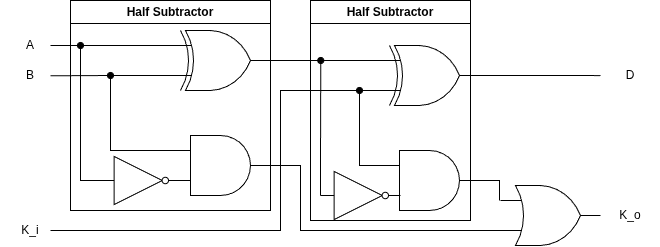

전감산기 (Full Subtractor)

전감산기는 한 자리 2진수 2개와 다음 자릿수의 빌림수$(K_{i})$를 입력하여 차$(D)$과 이전 자릿수로의 캐리$(K_{o})$의 출력을 갖는 뺄셈 회로이다.

전감산기는 2개의 반감산기를 활용하여 회로를 구성할 수 있다.

불 대수 함수

$D=A\oplus B \oplus K_{i}$

$K_{o}=K_{i} \cdot (\overline{A \oplus B}) + \overline{A} \cdot B$진리표

입력($A$) 입력($B$) 입력($K_{i}$) 출력($D$) 출력($K_{o}$) 0 0 0 0 0 0 0 1 1 1 0 1 0 1 1 0 1 1 0 1 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1

가감산기

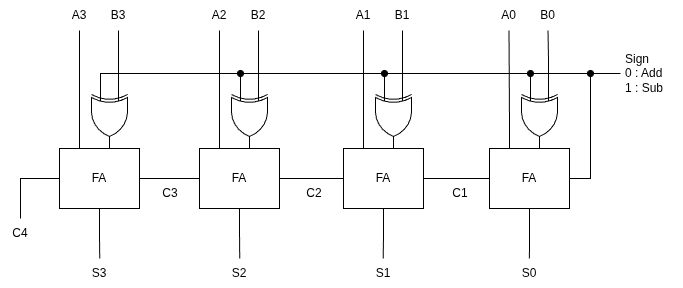

가감산기는 하나의 회로에서 덧셈과 뺄셈을 동시에 수행할 수 있는 회로이다. 2진수의 뺄셈이 2진수 덧셈 결과의 2의 보수인 점을 활용해 구성할 수 있다. 4-Bit 가감산기는 다음과 같다.

비교기

비교기는 두 2진수 값의 크기를 비교하는 회로이다. 회로는 $A=B$, $A\neq B$, $A > B$, $A < B$ 를 출력한다.

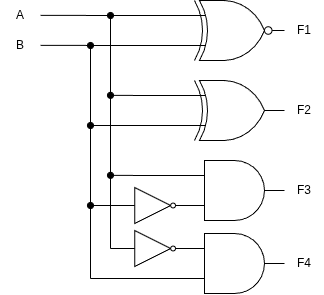

1bit 비교기의 회로 구성은 다음과 같다. 2bit, 4bit 등 데이터의 크기에 따라 비교기 회로를 구성할 수 있으며, 4bit 비교기는 대표적으로 7485 IC가 있다.

불 대수 함수

$F_{1}=\overline{A\oplus B}$

$F_{2}=A\oplus B$

$F_{3}=A \cdot \overline{B}$

$F_{4}=\overline{A} \cdot B$진리표

입력($A$) 입력($B$) 출력($F_{1}$) 출력($F_{2}$) 출력($F_{3}$) 출력($F_{4}$) 0 0 1 0 0 0 0 1 0 1 0 1 1 0 0 1 1 0 1 1 1 0 0 0