임베디드 스터디 - 순서논리회로 - 1

이번 글 참고자료:

한빛아카데미, 디지털 논리회로4판

ElectronicsTutorials

순서논리회로

- 조합논리회로와 달리, 순서논리회로는 상태가 존재하여, 동일한 입력에도 회로의 현재 상태에 따라 출력이 달라진다. 즉, 현재 상태를 저장하는 일종의 메모리가 존재한다.

- 조합논리회로와 마찬가지로 Universal Gates로 모든 회로를 표현할 수 있고, 회로의 동작 표현 또한 동일한 방식을 사용한다.

순서논리회로 분류

- 이벤트 기반 동작 (Event Driven) : 회로에 신호가 입력되면 즉각적으로 상태가 변화한다. (비동기 회로)

- 클럭 기반 동작 (Clock Driven) : 회로에 신호가 입력되어도 전체 시스템의 동작 클럭이 발생해야 상태가 변화한다. (동기 회로)

펄스 기반 동작 (Pulse Driven) : 회로의 상태 업데이트가 전체 시스템의 특정 신호에만 반응한다.

- 순회 동작 (Cyclic Circuit) : 회로의 동작 상태가 리셋되거나 마지막 상태에서 신호를 입력 받는 경우 초기 상태로 복귀할 수 있다.

- 비순회 동작 (Non-cyclic Circuit) : 회로의 동작 상태가 원상태로 복귀하지 않고, 한 방향으로만 진행한다.

래치 회로

대표적인 비동기 동작 순차논리회로. 쌍안정 상태(Bi-stable, 0, 1 두 개의 안정적 상태를 갖는 상태)를 갖는다.

실무에서 바운싱 영향을 제거하기 위한 디바운싱 회로로 자주 사용된다.

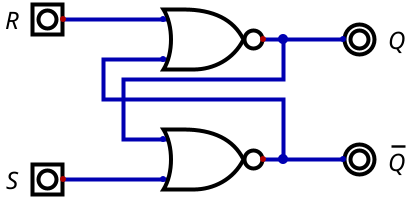

NOR SR 래치 회로

동작 설정

$S=0, R=0$: 상태 유지 (Hold) $S=0, R=1$: 리셋 (Reset) → $Q_{t+1}=0$ $S=1, R=0$: 셋 (Set) → $Q_{t+1}=1$ $S=1, R=1$: 금지 상태 (Forbidden) → $X$

진리표

입력($S$) 입력($R$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 X 1 1 1 X

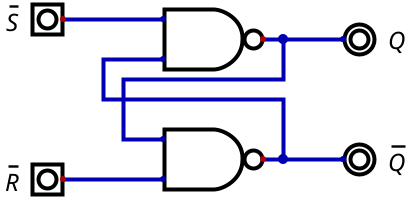

NAND SR 래치 회로

동작 설정

$\overline{S}=0, \overline{R}=0$: 금지 상태 (Forbidden) → $X$ $\overline{S}=0, \overline{R}=1$: 셋 (Set) → $Q_{t+1}=1$ $\overline{S}=1, \overline{R}=0$: 리셋 (Reset) → $Q_{t+1}=0$ $\overline{S}=1, \overline{R}=1$: 상태 유지 (Hold)

진리표

입력($\overline{S}$) 입력($\overline{R}$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 X 0 0 1 X 0 1 0 1 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1

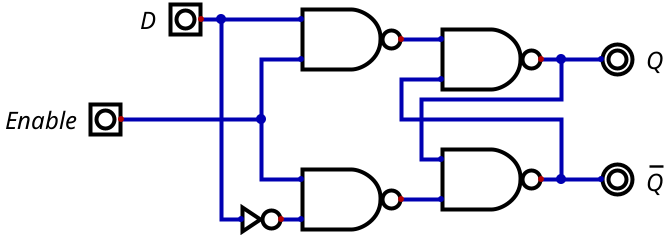

D 래치 회로

- SR 래치 회로에서 금지상태를 제거한 순서논리회로. S와 R의 입력을 무조건 다른 신호로 입력하고, Enable 신호를 통해 활성화한다. SR 래치와 다르게 Enable로 동작하는 동기 순서논리회로이다.

동작 설정

$E=0$: 상태 유지 (Hold) — Enable 비활성화 $E=1, D=0$: 리셋 → $Q_{t+1}=0$ $E=1, D=1$: 셋 → $Q_{t+1}=1$

진리표

입력($E$) 입력($D$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 1 1 0 0 0 1 0 1 0 1 1 0 1 1 1 1 1

플립플롭 (FF, Flip-Flop)

FF는 래치 회로에서 시스템 클럭을 따라 동작을 수행하는 동기 순서논리회로이다. FF는 특성 방정식, 진리표로 동작을 표현한다.

클럭 트리거

FF는 클럭 신호를 수신할 때 어떤 신호에 동작하는가에 따라 트리거의 형태가 달라진다. 트리거는 레벨 트리거, 엣지 트리거가 있다.

레벨 트리거 : 클럭 신호의 상태에 따라 동작한다. Ex) 클럭이 1(High) 일 때 FF가 동작한다. 한 번의 클럭에 FF가 여러번 동작할 수 있는 단점이 있다.

엣지 트리거 : 클럭 신호의 변화에 따라 동작한다. 레벨 트리거의 연속 동작 단점을 보완한다. $0$ → $1$의 변화에서 동작하는 트리거를 상승 엣지 트리거, $1$ → $0$의 변화에서 동작하는 트리거를 하강 엣지 트리거라 한다.

동작 특성

전파 지연 시간 (Propagation delay time)

FF에 입력 신호가 가해진 후 출력 신호에 변화가 일어날 때까지의 시간 간격 입력 신호(PRESET, CLK)의 50% 영역에서 출력 신호의 50% 영역까지의 시간 간격이다.

- $t_{PLH}$ : 신호 입력 후 출력 논리 0에서 출력 논리 1까지의 시간 간격

- $t_{PHL}$ : 신호 입력 후 출력 논리 1에서 출력 논리 0까지의 시간 간격

셋업 시간 (Set-up time)

FF의 클럭 트리거 발생 전에 입력 데이터가 유지되어야 하는 최소 시간이다.

- Set-up time violation : 클럭 트리거가 입력 데이터의 유지 시간보다 빠르게 입력될 경우 발생한다. 클럭 주파수를 낮춰 해결할 수 있다. 단, 클럭 주파수를 낮추면 전체 시스템의 성능이 떨어진다.

홀드 시간 (Hold time)

FF의 클럭 트리거 발생 후에 입력 데이터가 유지되어야 하는 최소 시간이다.

- Hold time violation : 입력 데이터가 유지 시간보다 빠르게 입력될 경우 발생한다. 데이터 입력에 버퍼를 추가하거나 지연시켜 해결할 수 있다. Hold time violation은 버퍼나 데이터 지연으로 인해 문제가 발생할 수 있기에 최우선적으로 해결해야하는 이슈이다.

펄스 폭 (Pulse width)

FF의 원활한 트리거 동작을 위한 클럭, Clear, Preset 신호의 최소 펄스 폭($t_{w}$)을 의미한다.

최대 클럭 주파수 (Maximum clock frequency)

FF가 안정적으로 동작할 수 있는 최대 클럭 주파수($f_{max}$)이다. 시스템 설계 시, FF가 최대 클럭 주파수 이하로 동작하도록 고려해야한다.

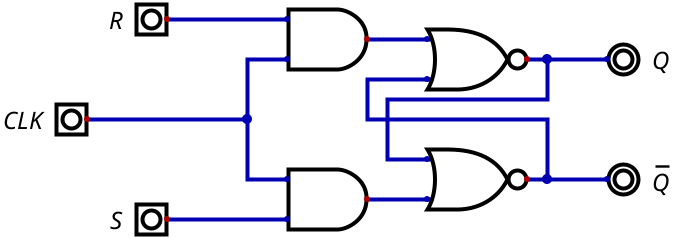

SR 플립플롭

- SR-FF은 SR 래치에 클럭 입력을 추가한 플립플롭이다. S는 Set, R은 Reset의 약자이다.

특성 방정식

$Q_{t+1} = S + \overline{R} \cdot Q_{t}, \quad (S \cdot R = 0)$

진리표

입력($S$) 입력($R$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 X 1 1 1 X

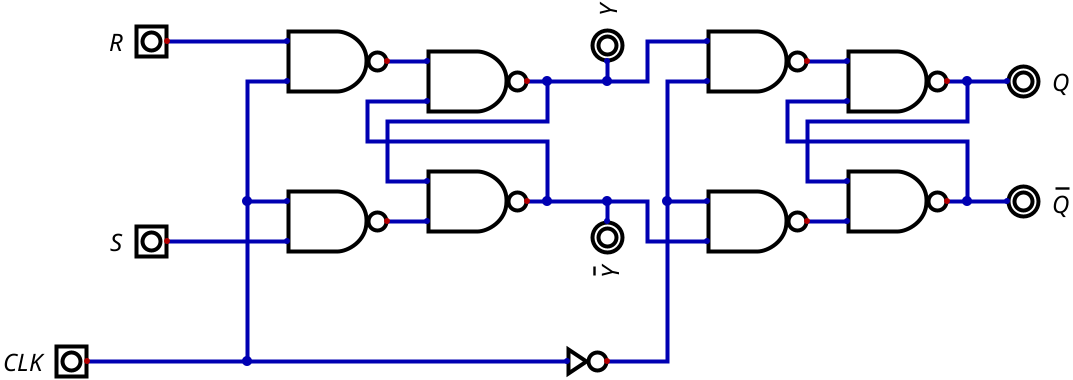

Master-Slave SR 플립플롭

- 레벨 트리거형 플립플롭의 문제를 보완하기 위해 사용되는 형태의 SR 플립플롭. SR 플립플롭 2개를 캐스케이드 형태로 연결하여 사용한다. Master-Slave 형태는 클럭 High 구간 동안 입력이 변화하면 의도치 않은 상태가 Master에 포착될 수 있다는 점(1’s Catching 문제)에서 단점이 있다.

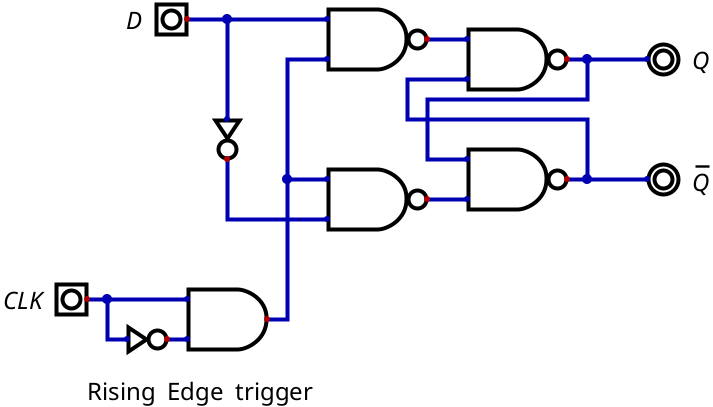

D 플립플롭

- D-FF은 D 래치에서 엣지 트리거 클럭 입력을 사용하는 플립플롭이다. D 플립플롭은 데이터의 지연, 데이터의 저장 역할을 하는 플립플롭으로, D는 Data, Delay에서 유래한다.

특성 방정식

$Q_{t+1} = D$

진리표

입력($D$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 1 0 1 0 1 1 1 1 D-FF는 $\overline{D}$의 입력을 Feedback 신호로 입력하여 클럭의 주파수를 반으로 줄여주는 기능으로도 사용할 수 있다.

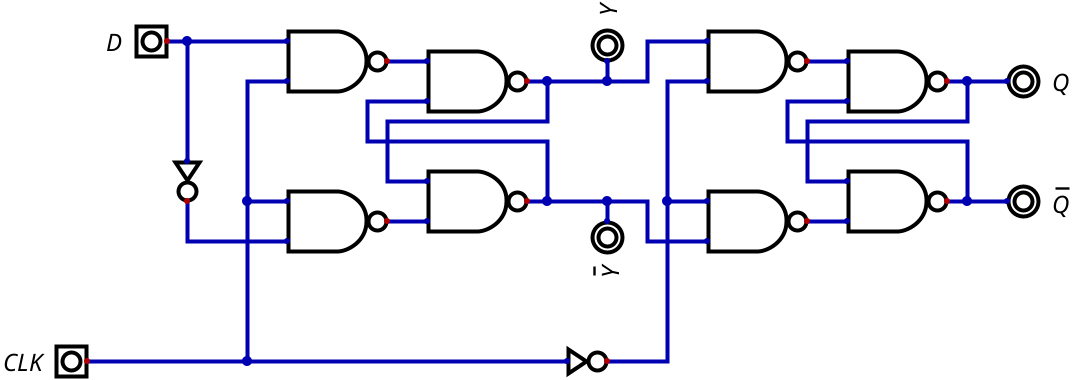

Master-Slave D 플립플롭

- 레벨 트리거형 플립플롭의 문제를 보완하기 위해 사용되는 형태의 D 플립플롭. D 래치 2개를 캐스케이드 형태로 연결하여 사용한다. Master-Slave 형태의 단점은 모두 동일하다.

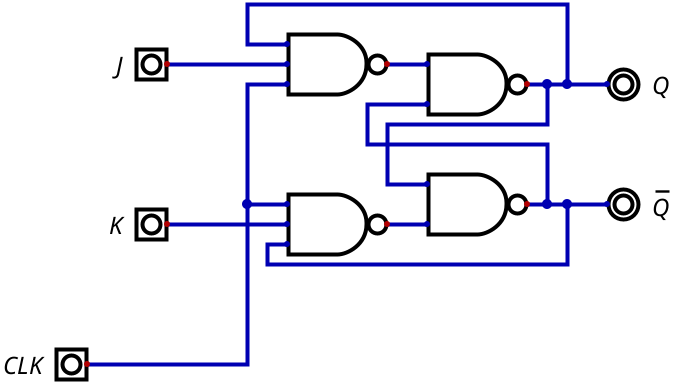

JK 플립플롭

- SR 플립플롭의 문제점(금지 상태 출력)을 보완하기 위한 순서논리회로. J는 SR-FF의 S, K는 SR-FF의 R에 대응하는 입력 신호이다. SR-FF와 다른 점은 $J=1, K=1$ 상태 일 때 출력이 이전 상태의 보수 값이 나온다는 점이다.

특성 방정식

$Q_{t+1} = J \cdot \overline{Q_{t}} + \overline{K} \cdot Q_{t}$

진리표

입력($J$) 입력($K$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 0

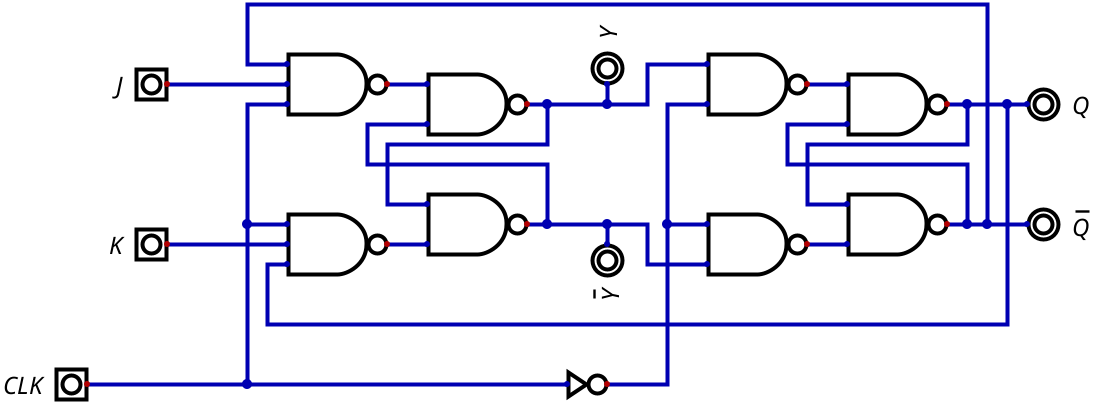

Master-Slave JK 플립플롭

- 레벨 트리거형 플립플롭의 문제를 보완하기 위해 사용되는 형태의 JK 플립플롭. JK 플립플롭 2개를 캐스케이드 형태로 연결하여 사용한다. Master-Slave 형태의 단점은 모두 동일하다.

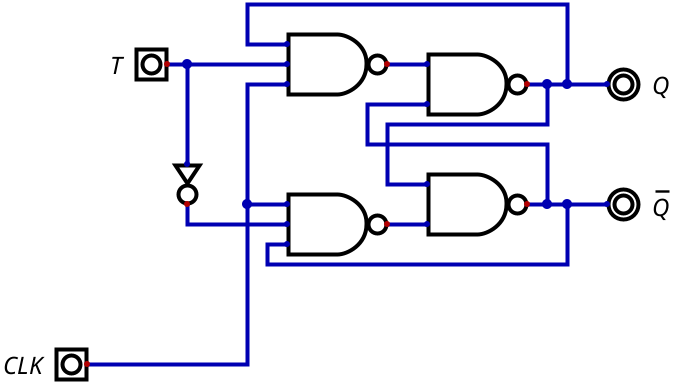

T 플립플롭

- JK 플립플롭의 J와 K 입력을 묶어서 한 입력 신호 T로 동작시키는 플립플롭. $T=1$ 일 때, 이전 상태의 보수를 출력한다. T는 Toggle에서 유래한다. T는 1로 고정시키고 클럭 입력을 받게되면 입력 클럭 주파수를 반으로 줄여주는 기능으로 동작한다.

특성 방정식

$Q_{t+1} = T \oplus Q_{t}$

진리표

입력($T$) 현재 상태($Q_{t}$) 다음 상태($Q_{t+1}$) 0 0 0 0 1 1 1 0 1 1 1 0